简介

D 触发器是指由时钟边沿触发的存储器单元,锁存器指一个由信号而不是时 钟控制的电平敏感的设备。锁存器通过锁存信号控制,不锁存数据时,输出端的信号随输入信号变化,就像信号通过缓冲器一样,一旦锁存信号起锁存作用,则数据被锁住,输入信号不起作用。

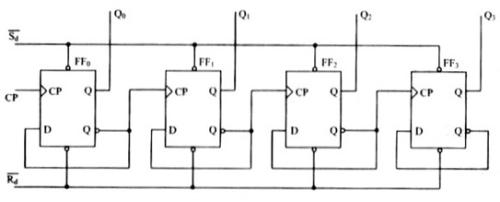

寄存器:在实际的数字系统中,通常把能够用来存储一组二进制代码的同步时序逻辑电路称为寄存器。由于触发器内有记忆功能,因此利用触发器可以方便地构成寄存器。由于一个触发器能够存储一位二进制码,所以把 n 个触发器的时钟端口连接起来就能构成一个存储 n 位二进制码的寄存器。

***一种时钟电路是波动式,即一个触发器的输出用作另一个触发器的时钟输入。

早期可编程器件只能实现同步时序电路,在CPLD器件中各触发器的时钟可以异步工作,有些器件中触发器的时钟还可以通过数据选择器或时钟网络进行选择。此外,OLMC内触发器的异步清零和异步置位也可以用乘积项进行控制,因而使用更加灵活

这些复位信号和FPGA内部信号的变化比起来是比较慢的。复位按钮**快也会到达毫秒级别,而FPGA内部信号都是纳秒级别的变化。全局复位的周期远大于系统时钟的周期,是完全可以保证所有的触发器被成功复位的。

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

多位触发器提供了一种智能方法,可在不影响时序的情况下降低设计的总体功耗。多位触发器的使用通过减少时钟树单元并保持设计中所需的缓冲器来降低泄漏功率和动态功率。它还有助于通过减小标准单元面积来改善设计密度,从而优化尺寸。

随着系统时钟频率的提高,并不是所有的触发器都能在同一个时刻从复位状态被释放。

直接用反相器加传输门设计,20个管子就能设计出建立时间和输出延迟都很低的D触发器,而且如果不考虑输出带载能力,所有n管都可以用**小尺寸,何必用这种结构呢,,,而且里面还有一个三输入的与非门,扇入有点大,,,

在亚稳态期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

555 集成电路内部有几十个元器件,有分压器、比较器、触发器、输出管和放电管等,电路比较复杂,是模拟电路和数字电路的混合体。它的性能和参数要在非线性模拟集成电路手册中才能查到。

对于大多数想要自己创作的玩家,特别是对编程有兴趣的青少年来说,scratch等UGC平台的门槛过高,而《乐高?无限》的触发器正是为玩家打造的一款简易编程工具,值得关注的是,它还是***在手机端就能操作的游戏触发器。它的使用逻辑也较为简单,玩家只需要将自己的创意拆解成为事件、动作、条件三个基本元素,就能够完成一次“游戏编程”!

影响动态功耗的一个重要因素:翻转率。降低翻转率,就可以动态功耗。D触发器的翻转是根据时钟上升沿或者下降沿来翻转的,那么就有牛人想到如果在D触发器需要保持不变的时候,我不让时钟翻转,那么D触发器就不会翻转,不就降低了翻转率从而降低了动态功耗了么?

锁存器电平触发会把输入端的毛刺带入输出;而触发器由于边沿作用可以有 效抑制输入端干扰。

我们可以看到,***级触发器虽然产生了亚稳态,但是由于第二级触发器的存在,亚稳态并没有传播下去,得到的复位信号依然是干净的,只不过这个复位信号可能延长多一个周期而已(这是因为亚稳态稳定后的可能态引起的)。