简介

亚稳态是指触发器无法在某个规定的时间段内到达一个可以确认的状态。使用两级触发器来使异步电路同步化的电路其实叫做“一步同位器”,他只能用来对一位异步 信号进行同步。两级触发器可防止亚稳态传播的原理:假设***级触发器的输入不满足其建立保持时间,它在***个脉冲沿到来后输出的数据就为亚稳态,那么在下 一个脉冲沿到来之前,其输出的亚稳态数据在一段恢复时间后必须稳定下来,而且稳定的数据必须满足第二级触发器的建立时间,如果都满足了,在下一个脉冲沿到 来时,第二级触发器将不会出现亚稳态,因为其输入端的数据满足其建立保持时间。同步器有效的条件:***级触发器进入亚稳态后的恢复时间 + 第二级触发器的建立时间 < = 时钟周期。

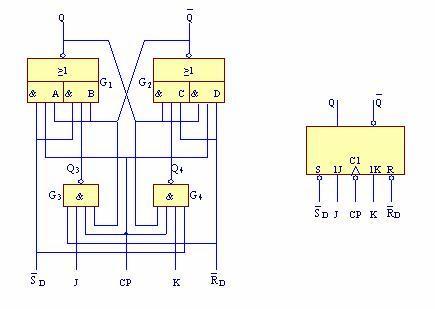

时序逻辑电路由组合逻辑电路和存储电路两部分组成。存储部分通常就由触发器组成。基于D触发器的时钟触发特性和保持特性,用触发器保持电路的临时状态值,在触发器的输入端接入组合逻辑电路,用于实现逻辑功能,再将组合逻辑的输出连接到需要触发器的输入端口中,在下一个时钟的上升沿,触发器在次采样保持该组合逻辑的输出,由此构成了基于历史状态时序逻辑电路。

锁存器是异步的,就是说在输入信号改变后,输出信号也随之很快做出改变 非常快。而另外一方面,***许多计算机是同步的,这就意味着所有的时序电路 的输出信号随着全局的时钟信号同时做出改变。触发器是一个同步版锁存器。

在代码中可以非常直接地设计双沿触发的触发器,下面这个代码示例就通过一个简单的移位寄存器对此进行了展示。注意这个例子中的输入信号在时钟的上升沿被采集,接着被送入双沿触发器。

持续记录,或者通过创建高级触发器(基于消息、数据信号值、错误消息、外部触发器的上下阈值和输入/输出信号)来触发记录。

在做DFT的时候,如果异步复位信号不能直接被I/O引脚驱动,就必须将异步复位信号和后面的的被驱动电路断开,用来保证DFT扫描和测试能够正确进行。两个同步复位触发器不应该包含在扫描链种,需要手动测试。

当在时钟域之间传递一个控制信号时,如果遵循其他规则(下面描述),则简单的双触发器同步器通常就足够了。

定时触发业务 - 定时执行的业务具有执行时间固定,执行期占用资源,不执行无需占用资源,以及业务逻辑稳定的特点。通过函数平台,开发人员可以将业务逻辑封装为函数服务,配合定时触发器触发函数执行,在需要的时候分配资源运行函数,执行完成释放资源,并且可以根据资源的空闲情况来分配更多函数实例增加并行执行能力。实现诸如数据加工处理,数据存储,报表数据生成等定时业务场景

直接用反相器加传输门设计,20个管子就能设计出建立时间和输出延迟都很低的D触发器,而且如果不考虑输出带载能力,所有n管都可以用**小尺寸,何必用这种结构呢,,,而且里面还有一个三输入的与非门,扇入有点大,,,

理论上,在高电平期间的 的那一个小扰动不应该影响**终的输出——触发器应该在时钟的下降沿工作,而那一刻对应的是 。因此, 应该保持在0。然而,却发现 变成了1。

这样,通过改变RC的参数,就可以自定义高电平的时间,达到自定义计时的功能,而对于555定时器组成的其他电路如多谐振荡器,施密特触发器,压控振荡器等,其分析与计算方法都与上无太大差别,只要一步一步的分析,多走几遍,你就会对其原理慢慢的熟悉起来。

影响动态功耗的一个重要因素:翻转率。降低翻转率,就可以动态功耗。D触发器的翻转是根据时钟上升沿或者下降沿来翻转的,那么就有牛人想到如果在D触发器需要保持不变的时候,我不让时钟翻转,那么D触发器就不会翻转,不就降低了翻转率从而降低了动态功耗了么?