简介

*通过一阶的触发器,输出的采样数据存在亚稳态的问题,因此需对采样点作进一步的处理。这里可将四个采样点通过进一步的触发,除掉亚稳态的问题,从而使采样点移到下一个相同的时钟域。通常,亚稳态的去除要经过两三级的处理,这就使得在有效数据输出前会有数位无效的数据,在数据采样的***个阶段,电路检测数据线上数据的传输。当检测到有数据传输时,对传输数据的有效性进行确认。确认数据有效后,输出高电平来指示采样点有数据传输。

***一种时钟电路是波动式,即一个触发器的输出用作另一个触发器的时钟输入。

在代码中可以非常直接地设计双沿触发的触发器,下面这个代码示例就通过一个简单的移位寄存器对此进行了展示。注意这个例子中的输入信号在时钟的上升沿被采集,接着被送入双沿触发器。

脉冲技术中广泛应用的非线性变换电路还有施密特觖发器、单稳态触发器和双稳态触发器等。采用施密特触发器可以将正弦波、三角波等任意波形的输入信号变换成边沿陡峭的矩形脉冲。采用单稳态触发器可以形成以输入脉冲的某一边沿(上升沿或下降沿)作时间基准的特定脉宽的信号。采用双稳态触发器则可对输入脉冲进行分频,构成各种计数器、分频器等等。

这些复位信号和FPGA内部信号的变化比起来是比较慢的。复位按钮**快也会到达毫秒级别,而FPGA内部信号都是纳秒级别的变化。全局复位的周期远大于系统时钟的周期,是完全可以保证所有的触发器被成功复位的。

这个同步器就是两级d触发器,其时钟为时钟域2的时钟。这样做是怕时钟域1中的这个信号,可能不满足时钟域2中触发器的建立保持时间,而产生亚稳态,因为它们之间没有必然关系,是异步的。

在FPGA的设计中,全局的清零和置位信号必须经过全局的清零和置位管脚输入,因为他们也属于全局的资源,其扇出能力大,而且在FPGA内部是直接连接到所有的触发器的置位和清零端的,这样的做法会使芯片的工作可靠、性能稳定,而使用普通的IO脚则不能保证该性能。

亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。

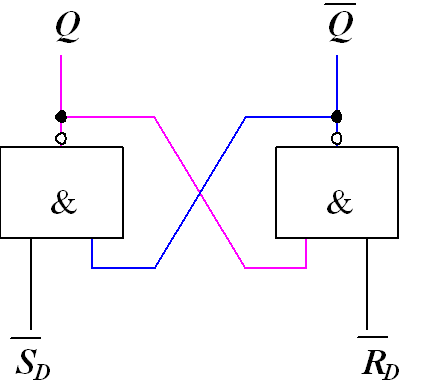

该类电路,即数字电路中的基本RS触发器、同步RS触发器、同步D触发器、主从触发器、边缘触发器等和在此基础之上的时序逻辑电路,而整个数字电路的大厦,也即由组合逻辑电路和时序逻辑电路所构成。

触发器有三个过程:先触发,接着是恢复,后面是稳定过程。他把电路改成双边触发,信号反相送到电路两边,这边推,那边拉,合力完成翻转,彻底防范干扰影响,推拉触发器的概念就此产生。

检测电路检测到0点时,输出脉冲给一个 D触发器 了 之类的触发器 ,保证该触发器输出在下一次 过0检测脉冲输出时 保持住 就像之前答主说的,一个半周期的节拍器。这样 该触发器的输出变成了 一个半周期内为高电平,再来一个半周期 反转 变为低电平,再来一个半周期 反转 变成高电平,以此类推。

理解了用户的动机和能力,设计适当的触发器**只完成了一半的工作。触发器可以帮助用户采取行动,提升用户的使用频率。但是用户行动之后的体验也是关键,这决定了用户是否会重复类似的行动。

根据 FBM,当用户可以采取行动时,触发器可能促使用户行动,但当用户没有能力或动机去行动时,触发器也没有作用。如果用户受伤了,并且对马拉松没有很大的兴趣,那么触发器并不能够促使他去跑步。FBM 致力于使用户处在可***的状态,这一点可以通过增强用户动机或者能力来实现。

T触发器是一类偏功能性的触发器——它没有做出任何***的改进,而只是提供了一种特殊的逻辑功能。我们将同一个输入赋给JK触发器的 和 :