简介

要知道:微分积分电路功能;555定时器各引脚功能、阈值输入端及输出端电压的逻辑规律;单稳态触发器、多谐振荡器和施密特触发器三种电路的基本功能。 会选用:实现脉宽定时,延时控制脉冲,脉宽调制、波形变换、整形、声响电源、时钟脉冲、标准时基脉冲信号等功能的电路结构类型。 会识别:各类结构单稳态触发器对输入触发脉宽的要求和有效触发的沿口类型。

毛刺并不是对所有的输入都有危害,例如D触发器的D输入端,只要毛刺不出现在时钟的上升沿并且满足数据的建立和保持时间,就不会对系统造成危害,我们可以说D触发器的D输入端对毛刺不敏感。 根据这个特性,我们应当在系统中尽可能采用同步电路,这是因为同步电路信号的变化都发生在时钟沿,只要毛刺不出现在时钟的沿口并且不满足数据的建立和保持时间,就不会对系统造成危害。 (由于毛刺很短,多为几纳秒,基本上都不可能满足数据的建立和保持时间)

我们可以看到***级触发器产生了亚稳态,但是由于第二级触发器的存在,亚稳态没有传播下去;虽然第二级触发器的复位信号撤离也在时钟有效沿附近,但是跟第一种情况一样,第二级触发器是不会产生亚稳态的。因此即使是极端状态,输出的复位信号也是干净的。

***个触发器将异步输入信号采样到新的时钟域,并等待一个完整的时钟周期,以允许***级输出信号上的任何亚稳态衰减,然后通过相同的时钟将***级信号采样到 第二级触发器,其目标是第2级信号现在是一个稳定且有效的信号,同步到新的时钟域。

本章在整本书中占有非常重要的比重,主要是讲解同步和异步两种时序逻辑电路。首先,了解时序逻辑电路的基本概念,区分同步和异步,了解三个基本方程组(激励、转换、输出)。接下来对同步时序电路进行分析,掌握分析的一般步骤,分析后进行设计,需掌握设计的一般步骤。然后便是异步时序电路的分析,同样要掌握分析的一般步骤。***有几个典型的时序逻辑电路需要熟练掌握,寄存器和移位寄存器、计数器。四五六章是本书的重点,尤其是要熟练地利用触发器分析并设计时序逻辑电路。

FPGA芯片有固定的时钟路由,这些路由能有减少时钟抖动和偏差。需要对时钟进行相位移动或变频的时候,一般不允许对时钟进行逻辑操作,这样不仅会增加时 钟的偏差FPGA设计中对时钟的使用?(例如分频等)和抖动,还会使时钟带上毛刺。一般的处理方法是采用FPGA芯片自带的时钟管理器如PLL DLL或DCM,或者把逻辑转换到触发器的D输入(这 些也是对时钟逻辑操作的替代方案)。

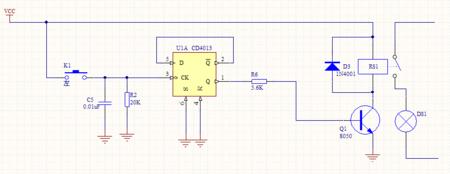

用一个按钮:如果用户用一个自复位按钮实现变频器的启/停控制,则需要在变频器中用自由功能块实现这一功能。因为自复位按钮给出的是脉冲信号,而自变频器的启动是高电平,停止是低电平,脉冲信号送到P554中是无法控制变频器的启/停,实现这一功能需要在变频器中用自由功能块中的D-触发器。

使用同步复位可能使综合工具无法分辨分辨复位信号和其他控制信号,导致进行复位的控制逻辑远离触发器(也就是说,并不是所以的ASIC库都有内置的同步复位逻辑,综合工具可能把符合逻辑综合到触发器自身之外)。例如对于带同步复位和加载使能的触发器,代码如下所示:

触发器实际上就是脉冲电路中的双稳电路,它的电路和功能都比门电路复杂,它也可看成是数字逻辑电路中的元件。目前也已有集成化产品可供选用。常用的触发器有D触发器和J—K触发器。

多谐振荡器又称为无稳态触发器,它没有稳定的输出状态,只有两个暂稳态。在电路处于某一暂稳态后,经过一段时间可以自行触发翻转到另一暂稳态。两个暂稳态自行相互转换而输出一系列矩形波。多谐振荡器可用作方波发生器。

凡是结构形式上由两个同步触发器级联而成 且它们的时钟信号 cp 相位相反的触发器均为主从触发器。

D触发器可以由两个D锁存器构成,驱动时钟的相位相反,前面的D锁存器称为主锁存器,后面的D锁存器称为从锁存器,因此D触发器也可以称为主从触发器。