简介

如前所述,***的设计方案,如采用格雷码计数器,同步电路等,可以**减少毛刺,但它并不能完全消除毛刺。 毛刺并不是对所有输入都有危害,例如D触发器的D输入端,只要毛刺不出现在时钟的上升沿并且满足数据的建立和保持时间,就不会对系统造成危害。因此我们可以说D触发器的D输入端对毛刺不敏感。但对于D触发器的时钟端,置位端,清零端,则都是对毛刺敏感的输入端,任何一点毛刺就会使系统出错,但只要认真处理,我们可以把危害降到比较低直至消除。下面我们就对几种具体的信号进行探讨。

在任何设计中使用的每个触发器都具有指定的建立和保持时间,或者在时钟上升沿之前和之后法律上不允许更改数据输入的时间。该时间窗口被精确地指定为设计参数,以防止数据信号变得太接近于可能导致输出变为亚稳定的另一同步信号。

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计比较好采用***的时钟域。换句话说,只有一个**的网络可以驱动一个设计中所有触发器的时钟端口。虽然这样可以简化时序分析以及减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗ASIC进行原型验证。本章讨论一下在FPGA设计中多时钟域和异步信号处理有关的问题和解决方案,并提供实践指导。

异步复位的同步释放电路也称为复位同步器,这个方法是将外部输入的异步复位信号进行处理,产生另外一个适合用于后面电路的复位信号,这个处理后的复位信号能够异步复位电路中的触发器,又不会存在撤离问题(因为经过了同步);这个异步复位同步释放的处理电路和RTL代码如下所示:

脉冲技术中广泛应用的非线性变换电路还有施密特觖发器、单稳态触发器和双稳态触发器等。采用施密特触发器可以将正弦波、三角波等任意波形的输入信号变换成边沿陡峭的矩形脉冲。采用单稳态触发器可以形成以输入脉冲的某一边沿(上升沿或下降沿)作时间基准的特定脉宽的信号。采用双稳态触发器则可对输入脉冲进行分频,构成各种计数器、分频器等等。

异步复位:使用异步复位,不会在数据路径增加额外的逻辑门。异步复位的主要问题是复位释放。如果复位的释放发生在时钟边沿或者接近时钟边沿,则触发器可能进入亚稳态。

换个方式理解:需要建立时间是因为触发器的D段像一个锁存器在接受数据,为了稳定的设置前级门的状态需要一段稳定时间;需要保持时间是因为在时钟沿到来之后,触发器要通过反馈来所存状态,从后级门传到前级门需要时间。

在FPGA的设计中,全局的清零和置位信号必须经过全局的清零和置位管脚输入,因为他们也属于全局的资源,其扇出能力大,而且在FPGA内部是直接连接到所有的触发器的置位和清零端的,这样的做法会使芯片的工作可靠、性能稳定,而使用普通的IO脚则不能保证该性能。

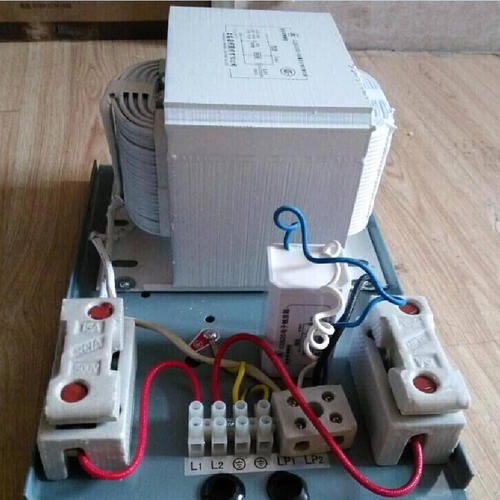

二次输出电压经过整流滤波后加到触发器上,当信号电压达到整定值时,触发器翻转(BG1截止,BG2导通)干簧继电器动作,动断触点打开,动合触点闭合。当任何一个输入电压(或电流)为零或很低时,产生的情况与两个电压(或电流)不同相时相同,继电器也应立即动作。

而“同步”是指计数器中的各触发器都受到同一时钟脉冲的控制,所有触发器的状态变化都在同一时刻发生。

生活离不开手机,当你的创意突然闪现时,也只需要拿起手机就可以记录这一刻!《乐高?无限》***实现了在移动端操作的触发器功能。它的出现为玩家创造了一个舒适和便捷的开发环境,手机端的触发器不仅可以实现复杂的逻辑,同时还能保持它的简洁性和延续性,让玩家的操作更方便快捷。