简介

延迟线使第二个触发器的触发稍晚于***个触发器,而使***个触发器的输出能够在第二个触发器接收到时钟信号之前稳定到有效的逻辑电平。延迟时间的选择要合适,从而使第二个触发器D输入处出现不确定电平的时间相对输入触发而言可忽略不计。上述方案是一种基本的实际触发电路。实际上,在一些特定场景的大部分触发示波器中都是采用的这种方案。示波器前面板上第三个触发控制装置(模式控制开关)所指的正常触发模式也就是它。

因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时 需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值。这就是为什么要用两级触发器来同步异步输入信号。这样做可以防止由于异步输入 信号对于本级时钟可能不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。

在任何设计中使用的每个触发器都具有指定的建立和保持时间,或者在时钟上升沿之前和之后法律上不允许更改数据输入的时间。该时间窗口被精确地指定为设计参数,以防止数据信号变得太接近于可能导致输出变为亚稳定的另一同步信号。

另一种流行的时钟电路是采用行波时钟,即一个触发器的输出用作另一个触发器的时钟输入。如果仔细地设计,行波时钟可以象全局时钟一样地可靠工作。然而,行波 时钟使得与电路有关的定时计算变得很复杂。行波时钟在行波链上各触发器的时钟之间产生较大的时间偏移,并且会超出**坏情况下的建立时间、保持时间和电路中 时钟到输出的延时,使系统的实际速度下降。

异步重置的比较大问题是它们是异步的,在复位阶段和解复位阶段(复位撤离)都是异步的。复位阶段不是问题,解复位才是问题。如果在触发器的活动时钟边缘或附近释放异步复位,则触发器的输出可能变为亚稳态,这样电路的复位状态可能会丢失,解复位失败。

不同的时钟域之间信号通信时需要进行同步处理,这样可以防止新时钟域中***级触发器的亚稳态信号对下级逻辑造成影响,其中对于单个控制信号可以用两级同步器,如电平、边沿检测和脉冲,对多位信号可以用FIFO 双口RAM,握手信号等。

在功能上,同步电路设计方式具有很多的好处:z 在同步系统中,只要电路系统在时序上完全收敛,电路设计中令人头疼的竞争和冒险现象,得到了有效的避免。z 由于触发器只有在时钟边缘才改变取值,这就很大限度的减少了整个电路受噪声影响的可能。

当控制信号穿过时钟域时,信号相对于目标时钟域为异步输入。因此,该信号需要同步以满足目的时钟域的建立和保持要求,否则触发器会进入亚稳态。

凡是结构形式上由两个同步触发器级联而成 且它们的时钟信号 cp 相位相反的触发器均为主从触发器。

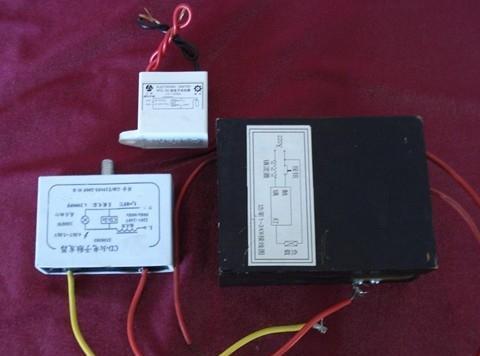

移相触发器采用独特的同步技术设计 不需外接同步变压器 接线简便.适用于单相、三相阻性或感性负载.宽脉冲触发方式稳定可靠.本仪器采用高性能的开关电源 可在极宽的电源波动范围内正常工作.控制输入与触发输出完全光电隔离 ***用于负载要求连续平滑调节低电压、大电流以及控制精度要求较高或不允许大电流冲击的单相、三相控制系统.如交流、直流电机调速等 具有很高的性价比.

在使用可编程逻辑过程中,具有乘积项逻辑阵列时钟(即时钟是由逻辑产生的),允许任意函数单独地,控制各个触发器。所以就出现了阵列时钟。

我们在确认了采用动态逻辑的触发器之后,接下来就是如果融入我们的设计流程。我们***在静态逻辑的触发器的功能描述上,增加了部分时间的约束,以防止动态逻辑中漏电流导致动态电容点漏电。并且在时序和功耗提库时,用静态触发器的一些参数进行套用。简单说,我们在动态逻辑上加了一个外框,让它在前端设计人员看来,就是一个正常的静态触发器,对于前端设计与综合,没有任何的不同。

所以,我们的结论就是,由于门电路的延时和触发器的电路结构,建立时间和保持时间是一定存在的,否则就不能满足触发器的功能要求。