简介

要知道:微分积分电路功能;555定时器各引脚功能、阈值输入端及输出端电压的逻辑规律;单稳态触发器、多谐振荡器和施密特触发器三种电路的基本功能。 会选用:实现脉宽定时,延时控制脉冲,脉宽调制、波形变换、整形、声响电源、时钟脉冲、标准时基脉冲信号等功能的电路结构类型。 会识别:各类结构单稳态触发器对输入触发脉宽的要求和有效触发的沿口类型。

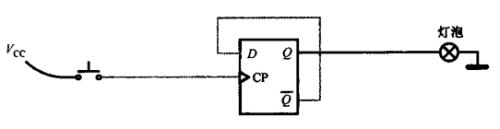

基本RS触发器只要输入信号变化,输出状态就会立即发生相应变化,这不但使得电路的抗干扰能力变差,也给多个触发器的同步工作带来不便。在实际应用中,通常要求触发器的状态按一定的时间节拍变化,即在时钟脉冲到达时,才根据输入信号改变状态;没有时钟信号时,即使输入信号改变,也不影响触发器的输出状态。为此,增加时钟脉冲输入端CP以及相应的输入控制电路,就有了同步RS触发器这一类数字芯片。

当异步复位信号的撤离时刻在时钟有有效沿附近时,就可能导致恢复时间或去除时间不足,即这个时候违背了复位恢复时间或去除时间,这时就可能导致触发器的输出端为亚稳态(注意是可能),如下所示:

在数字电路中,移位寄存器(英语:shift register)是一种在若干相同时间脉冲下工作的以触发器为基础的器件,数据以并行或串行的方式输入到该器件中,然后每个时间脉冲依次向左或右移动一个比特,在输出端进行输出。这种移位寄存器是一维的,事实上还有多维的移位寄存器,即输入、输出的数据本身就是一些列位。实现这种多维移位寄存器的方法可以是将几个具有相同位数的移位寄存器并联起来。

在代码中可以非常直接地设计双沿触发的触发器,下面这个代码示例就通过一个简单的移位寄存器对此进行了展示。注意这个例子中的输入信号在时钟的上升沿被采集,接着被送入双沿触发器。

**项:一种文物展柜**灯光控制器,设有壳体,其特征在于:所述壳体内设置有电路板,所述电路板上设有感应触发器模块、渐变调光控制器模块、时基单元电路模块、控制输出电路模块、电源模块,所述感应触发器模块与渐变调光控制器模块、控制输出电路模块通过数据线控制连接,所述感应触发器模块与时基单元电路模块、控制输出电路模块通过数据线控制连接,所述感应触发器模块、渐变调光控制器模块、时基单元电路模块、控制输出电路模块与电源模块供电连接。

根据各级触发器时钟端的连接方式可以将时序电路分为同步/异步。

在FPGA的设计中,全局的清零和置位信号必须经过全局的清零和置位管脚输入,因为他们也属于全局的资源,其扇出能力大,而且在FPGA内部是直接连接到所有的触发器的置位和清零端的,这样的做法会使芯片的工作可靠、性能稳定,而使用普通的IO脚则不能保证该性能。

计数器可分为异步计数器和同步计数器。所谓"异步计数器是指没有统一时钟脉冲控制,或者没有时钟脉冲控制,各触发器状态变化不是发生在同一时刻。

而CPLD的宏单元内一般含两个或两个以上的触发器,其中只要一个触发器与输出端相连,其余触发器的输出不与输出端相连,但能够经过相应的缓冲电路反应到与阵列,然后与其他触发器一起构成较杂乱的时序电路,这些不与输出端相连的内部触发器就称为[隐埋"触发跟着PLC技能的开展。

同步计数器中的同步是指各触发器受同一时钟脉冲的控制 。()

钟控D触发器其实就是D锁存器,边沿D触发器才是真正的D触发器,钟控D触发器在使能情况下输出随输入变化,边沿触发器只有在边沿跳变的情况下输出才变化。

我们可以看到,***级触发器虽然产生了亚稳态,但是由于第二级触发器的存在,亚稳态并没有传播下去,得到的复位信号依然是干净的,只不过这个复位信号可能延长多一个周期而已(这是因为亚稳态稳定后的可能态引起的)。